What to expect from the new DDR4 memory

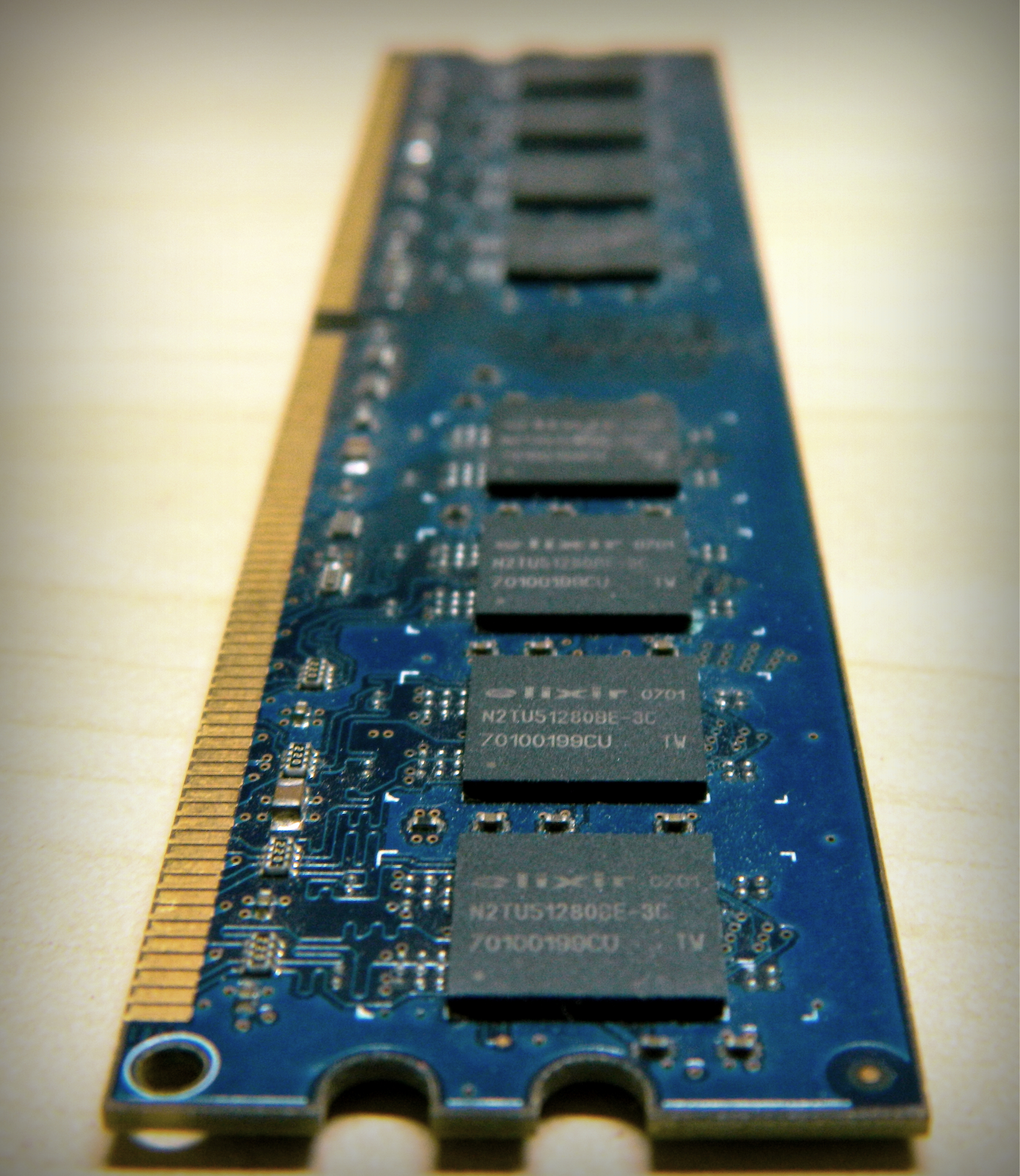

Just a few years ago the DDR3 RAM replaced the DDR2 at a very fast pace. As the need for more faster systems grows, the memory market evolves to suffice the demand of the consumer. Every 2-3 years we hit a limit where older systems no longer keep up to the rapidly developing technology which requires faster systems.

The advanced video processing requires fast enough system to render video. If that is rendered on a slow machine from 2007, it could take several hours just to process a few minutes worth of HD (high bit rate) video. With the 3D cameras coming out in market and also the growing demand for them has driven people to have faster systems because older systems cannot keep up with the high bit rate of 3D videos. Forget about editting them on a low end system, it could take ages. The new CPU architectures coming from intel and AMD have a bigger performance and it is a blessing on video producers as well as hardcore gamers. But making fast CPUs is not enough because, soon we are going to hit a wall where the bottleneck would be caused by the system memory (RAM). That wall is expected to be hit in few months to 1 year.

JEDEC has officially announced that they will be beginning to manufacture DDR4 chips by the year end (which is just few days away). This will kickstart the manufacturing of DDR4 memory and by mid 2013 we shall be having new memory modules ready for our system. But, it will still take about a year before new CPU’s are developed by Intel and AMD to handle the new DDR4 memory.

What is so special about the new DDR4 memory?

The main focus of DDR4 memory is power management. It will be enhanced with advanced power management system.

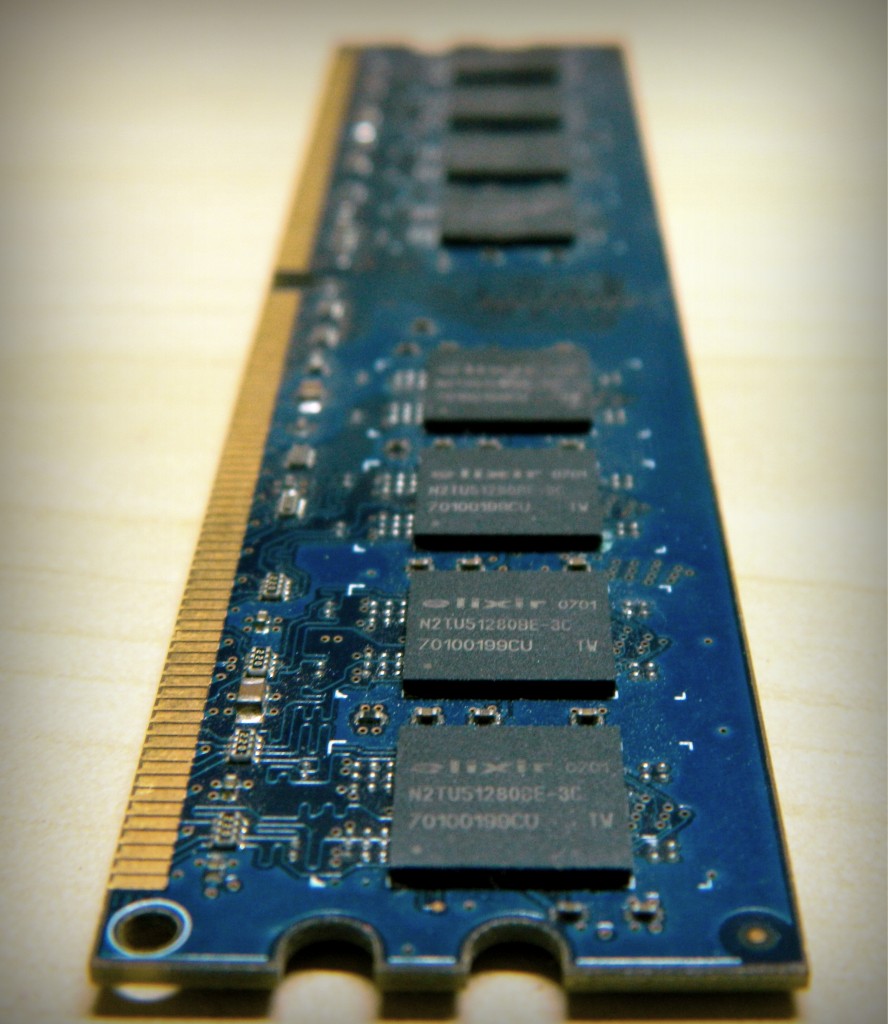

Lower voltages will be required for normal operations. Current DDR3 memory chips require 1.5 volts while the DDR4 will require on 1.2 volts. That is 20% reduction in voltage requirement. Normally, lower voltages always translate to lower power requirement. Thus, DDR4 will require lower power for its operation. Lower power translates to lesser heat!

The DDR4 would not be required by general consumer for sometime, but those who do a ton of video processing and hardcore gaming, DDR4 is for them! The current maximum bus speed for DDR3 is 1600 MHz while the lower frequency is 1333MHz. It is expected that the DDR4 will operate at a higher bus speed of 1866+ MHz to 2000MHz.

Bus speed is what actually matters the most because it is the frequency at which the CPU and the memory communicate. The CPU could be able to handle several GigaBytes of data per second, but having a low bus speed will bottleneck the true capacity of your CPU. A higher bus speed will enable more data to be processed in a given time slot.

DDR4 will be able to handle 3.2 billion transfers per second. This is double that of the current maximum transfers possible with high end DDR3 running at 1600 MHz bus speed.

New DDR4 will have deep power down mode which will put the memory module into sleep mode. This will require no refresh of the memory. It will also have facility for refreshing individual memory chips on the RAM module. Refreshing individual memory chips on DDR3 is not possible, which requires whole DIMM to be refreshed when only one of the chips need it.

The people having large amount of servers will be able to first make true use of the new DDR4 memory. Those people are always looking out for new technology which can reduce the power consumption and wanting more speed for their systems.

Additional features included in the new DDR4:

- Three data width offerings: x4, x8 and x16

- New JEDEC POD12 (1.2V) interface standard for DDR4

- Differential signaling for the clock and strobes

- Nominal and dynamic ODT: Improvements to the ODT protocol and a new Park Mode allow for a nominal termination and dynamic write termination without having to drive the ODT pin

- Burst length of 8 and burst chop of 4

- Data masking

- DBI: to help reduce power consumption and improve data signal integrity, this feature informs the DRAM as to whether the true or inverted data should be stored

- 512 K page size for x4 devices: reduces power (less activation power), and extends the usefulness of x4 devices, which allow for more efficient EDC solutions for high-end systems

- Programmable refresh: Reducing performance penalty of dense DDR4 devices by allowing for refresh intervals ranging from 1x to .0625x the normal refresh interval

- CRC computation/validation across the data bus: Enabling error detection capability for data transfers – especially beneficial during write operations and in non-ECC memory applications

- New CA parity for command/address bus: Providing a low-cost method (parity) to verify the integrity of command and address transfers over a link, for all operations

- Per-DRAM Addressability: Can uniquely select and program DRAMs within a memory structure

- DLL off mode supported

Currently, a single 1 Gbit DDR3 memory chip costs $1.4 while a 2Gbit memory chip costs $1.7. A single 4Gbit DDR4 memory costs upwards of $30. The price for the same DDR4 chip will reduce to $5 per chip when full scale manufacturing starts. Which will slowly go on reducing as the demands grow. At the same time, the DDR3 memory would begin to get expensive, just like it happened in case of DDR2. When DDR3 was out in the market, the price for DDR2 started to grow tremendously and the DDR3 has now become very inexpensive.

Voice of the people